获Linux支持的开源指令集RISC-V投身存储和AI领域

随着存储巨头西部数据 Western Digital (WD) 宣布支持 RISC-V 并投资 Esperanto Technologies,我们或许可以期待 RISC-V 指令集架构有望成为 ARM 和 x86 的可行替代方案……

随着存储巨头西部数据 Western Digital (WD) 宣布支持 RISC-V 并投资 Esperanto Technologies,我们或许可以期待 RISC-V 指令集架构有望成为 ARM 和 x86 的可行替代方案……

EETimes 消息,WD 宣布将在 RISC-V 处理器上实现标准化,并投资了一家初创公司 Esperanto Technologies -- 该公司主要采用开源指令集架构设计高级 SoC 和核心。从这两项举措来看,尽管 RISC-V 架构目前还不够成熟,但有望成为 ARM 和 x86 的可行替代方案。

WD 的 CTO Martin Fink 近日在第七届 RISC-V 工作组会议宣布该公司计划一年出货 10 亿以上的 RISC-V 核心。不过长远来看,WD 预计在其硬盘和固态硬盘(SSD)中每年可出货多达 20 亿个 RISC-V 架构芯片。看起来 WD 是想将 RISC-V 核心用于硬盘微控制器,它的部分产品此前整合了 ARM 核心的控制器。此外,WD 还私下透露正在研发用于推论的机器学习加速器,这可能与其投资 Esperanto 有关。至于 Esperanto 这家初创公司,它计划推出一系列 64 位的 RISC-V 芯片,其中包括:

采用台积电 7nm 工艺制造的人工智能“超级计算机芯片(supercomputer-on-a-chip)”

针对最高单线程性能的 16 核“ET-Maxion”

一个 4,096 核心的 ET-Minion

对此,有分析师表示,像 WD 这样的大公司在这个架构上下注是对 RISC-V 生态系统的巨大推动,并且有一家初创公司希望把它带到高端产品上,这更是件大事。因为到目前为止,RISC-V 主要仍着眼于底层的物联网和微控制器 (MCU)。

Esperanto 的首席执行官 David Ditzel 一直以来都力挺 RISC-V 指令集架构,同时也是业界微处理器的老手,曾在以前的升阳(Sun Microsystems)和初创公司 Transmeta 负责服务器处理器设计,在这之前还曾经短暂任职于英特尔。上月更早的时候,Linux 4.15 宣布支持加州伯克利开发的开源指令集架构 RISC-V。RISC-V 开发者 Palmer Dabbelt 在邮件列表上宣布,Linux 版 RISC-V 已被接受合并到 Linux 4.15,Linux 4.15 已支持 RISC-V 架构的代码,但还不支持硬件。

RISC-V 是基于精简指令集(RISC)原则的一个开源指令集架构。与大多数指令集相比,RISC-V 指令集可以自由地用于任何目的,允许任何人设计、制造和销售 RISC-V 芯片和软件。虽然这不是第一个开源指令集,但它具有重要意义,因为其设计使其适用于现代计算设备。有了 Linux 内核的支持,RISC-V 的普及度有望进一步提高。

此外还留意到有开发者在 GitHub 上发布了能让 RISC-V 获得 Rust 语言支持的工具 —— RISC-V Rust toolchain。Rust 是一门由 Mozilla 开发和维护的系统编程语言,它有着惊人的运行速度,能够防止段错误,并保证线程安全。Rust 语言的语法类似于 C/C++,提供了对高并发和高度安全的系统开发的支持,主要针对高并发和安全系统的开发,已经被用于许多领域,从微内核操作系统和加密货币到容器运行时,就连目前最新版的火狐浏览器 FireFox Quantum 也使用 Rust 语言重新编写了全新 CSS 引擎,性能翻倍。

RISC-V Rust toolchain 的开发者还使用了由 lowRISC 基金会开发的 RISC-V LLVM 构建自己的端口,以及发布了一个 Rust 库,为 HiFive1 板提供 BSP,并为其外围设备提供支持。

RISC-V在高性能计算与数据中心取得进展

2021年9月消息,RISC-V通常与嵌入式项目有关,而现在这个开源的ISA可能在更高端的计算市场上成为新的宠儿。RISC-V 基金会于 10 多年前在加州大学伯克利分校的实验室成立,因其在建立开源ISA中的革命性成功而闻名。该项目的初始目标是低功耗嵌入式处理器,但从那时起,RISC-V ISA已经有了很大的发展。自成立以来,该项目已发展到超过2000个成员,形成了与Linux基金会的战略伙伴关系,并为数百个行业和学术项目提供支持。

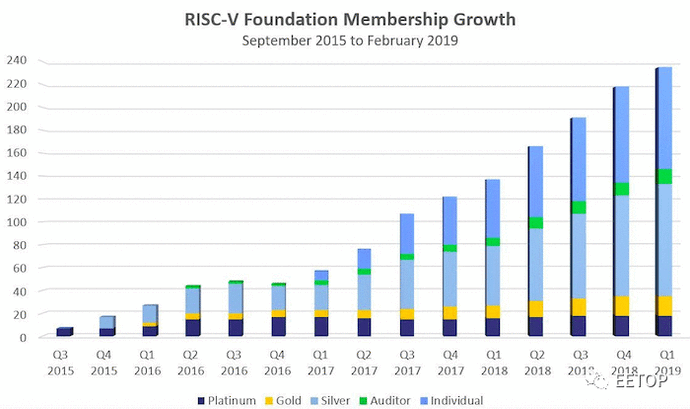

RISC-V基金会成员的增长

现在,RISC-V 进化的下一步是一个非常雄心勃勃的步骤:为高性能计算 (HPC) 开发 RISC-V。具体而言,RISC-V国际组织宣布,它希望将其影响力扩展到数据中心领域,重点关注包括机器学习在内的应用。

HPC 需要加速器和异构平台

从历史上看,HPC 需要两种主要信息处理方法的协作:串行和并行。

串行处理单元通常由 CPU 内核组成,以处理诸如操作系统和非常基本的应用程序之类的通用任务。并行处理单元往往由多个CPU或GPU组成,它们通过高带宽互连与内存模块聚集在一起构成集群。近年来,HPC 的两大趋势是增加了对加速器和异构平台的使用。

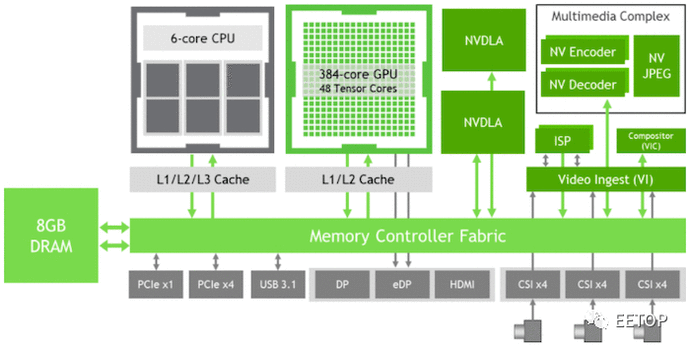

NVIDIA Jetson Xavier NX 是一个异构平台示例

加速器最近发现了巨大的价值,因为像ML这样的应用,其工作负载由ASIC来处理比GPU或CPU更好。对ASIC的依赖反过来又导致了异构计算的兴起:将CPU、GPU和加速器结合起来的计算架构。

为什么RISC-V适用于HPC?

对定制计算平台日益增长的需求为 RISC-V 进军 HPC 奠定了良好的基础。

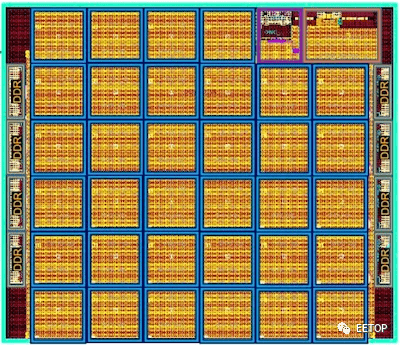

该项目的开源、可定制性质为工程师提供了大量资源和灵活性,可以利用现有资源并为其工作负载创建独特的解决方案。这就是 RISC-V 在初创公司中如此受欢迎的原因,包括那些冒险进入数据中心市场的公司。一个典型的例子是 Esperanto 的 ET-SoC-1 ML 推理芯片,该芯片。

ET-SoC-1 是基于 RISC-V 的 HPC 芯片

另一家初创公司 Ventana Micro SystemsInc. 也 开发了面向数据中心的多核 RISC-V 小芯片。据说这些 CPU 包括可扩展的指令集功能。

英特尔也对基于 RISC-V 的服务器表现出兴趣

尽管估计有多达 200 家初创公司在开发 AI/ML——其中一些依赖于 RISC-V——但这些小公司仍然面临英特尔等巨头的竞争。

彭博社最近的报道表明,即使是英特尔也可能对其服务器市场的 RISC-V 产生兴趣。6 月份英特尔据称提出以超过 20 亿美元的价格收购 RISC-V 芯片设计公司 SiFive。英特尔对 SiFive 以及 RISC-V 的兴趣可能源于去年英伟达试图收购 Arm。SiFive 是一项颇具吸引力的备份计划,适用于担心 NVIDIA 交易会损害他们目前对 Arm 芯片许可和工艺设计的访问的 Arm 客户。

RISC-V 宣布 HPC 计划

为了让 RISC-V 追求高性能计算,成立了RISC-V 高性能计算特别兴趣小组 (SIG-HPC)。

在该组织的网站上,SIG-HPC 的目标是在其 ISA 上启用包括天气预报、计算流体动力学、材料科学等在内的工作负载。为了做到这一点,该小组正在启动新的计划,例如将HPC软件生态系统映射到RISC-V。这包括发现哪些开源库、基准和应用程序目前可以在RISC-V ISA上开箱即用,并可能成为有用的工具来利用。

目前RISC-V SIG-HPC 由 141 名成员以及10名活跃的研究、学术和来自各种组织的工业成员组成。